在我们现有的功率半导体器件中,PN结占据了极其重要的地位,其正向阻断能力的优劣直接决定着功率半导体器件的可靠性及适用范围。

当PN结两边掺杂浓度为固定值时,一般认为除超级结(superjunction)之外,平行平面结的击穿电压在所有平面结中具有最高的击穿电压。

在实际半导体功率器件的制造过程中,一般会在PN结的边缘引入球面边界和柱面边界。该边界位置的击穿电压低于平行平面结的击穿电压,使半导体功率器件的击穿电压降低。

由于PN结边缘结构造成的曲率效应对PN结击穿电压有一定的负面影响,许多学者提出了一系列的结终端技术用以消除或者减弱球面结或柱面结的曲率效应。

下文对曲率效应的产生及一些新型结终端技术做简单介绍。

1、曲率效应的产生及其对击穿电压的负面影响

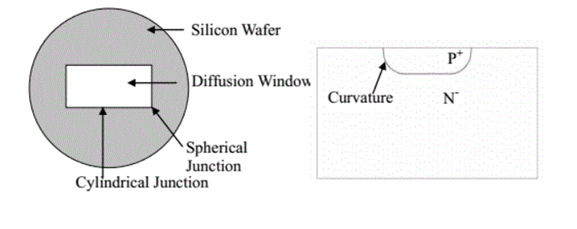

在半导体制造过程中,当通过矩形的掩膜进行扩散形成PN结时,PN结的构成成分包括中心位置的平板形结、边缘区的柱面结和掩膜弯角处的球面结(如图1-1)。

柱面结或球面结都会使PN结的击穿电压低于平行平面结的击穿电压。

图1-1 边缘区柱面结和球面结

常见的PN结中,通过掩膜扩入的异型杂质浓度一般远高于原有杂质浓度。在结面位置的p越小,击穿电压越低,当p趋近于无穷大时PN结的击穿电压趋近于平行平面结的击穿电压。

杂质在硅中的扩散为各向异性,热过程中杂质沿各不同方向进入硅材料,一部分杂质进入到原窗口位置下方,形成横向扩散。横向扩散的扩散量约为纵向扩散的扩散量的85%左右,经横向扩散形成的球面结或柱面结的曲率半径p可用横向扩散量r近似。

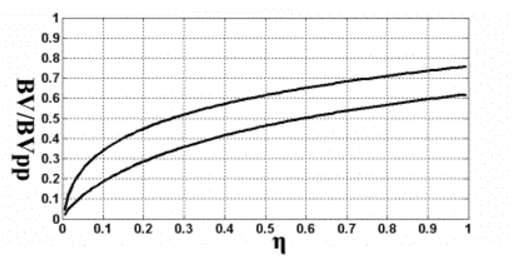

下图1-2反映了球面结及柱面结归一化击穿电压与标准化半径n的对应关系。

图1-2 归一化击穿电压与标准化半径η的对应关系

对于常规制造工艺,一般n的典型值只有0.1或0.1以下。球面结或柱面结对应的击穿电压只有理想平行平面结击穿电压的10%到20%左右,严重影响了高压器件的可靠性。

2、结终端技术

受实际制造的高压PN结边界位置的球面或柱面曲率效应的影响,结的击穿电压显著低于平行平面结的击穿电压。为改善结的击穿特性,可采用场板、场限制环、磨角等技术降低曲率效应的影响,提高PN结击穿电压。

其目的为降低半导体表面电场,尽量将雪崩击穿的可能性从半导体表面移向半导体内部,使PN结的击穿电压接近或达到理想平行平面结的击穿电压。

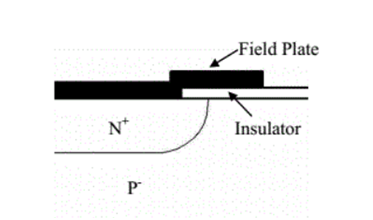

场板技术是改善PN结曲率效应最常用的手段之一,如图1-3。它是由与N+接触的金属延伸至N+P范围以外构成的。

图1-3 场板结构示意图

当PN结反偏时,场板电位相对P型区为高电位。若场板下的绝缘介质厚度合适,高电位的作用使P型硅表面耗尽,结耗尽区扩展至场板以下区域,表面靠近N+P结位置原有的高电场被分散,并在场板的边缘出现一个新的电场峰值。

最优化的设计要求场板边缘的电场峰值等于N+P结位置的电场峰值,可通过求场板下解绝缘介质中的Laplace方程和P型硅中的Possion方程计算出最佳场板长度。

当场板电位为独立的固定电位时,已有的报道表明NP结的击穿电压与场板电压成线性关系。

实际的制造过程中一般不方便为场板提供特定的固定偏置,场板常常与N+区域直接连接并电位相等。

计算表明,在场板下方的绝缘SiO2介质厚度小于0.7um和P型衬底浓度低于107cm3时雪崩击穿发生于场板边缘。为避免这一现象,场板结构衍生出斜坡场板、阶梯场板、电阻场板等新结构。

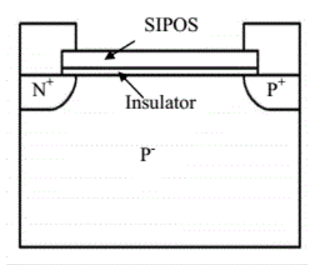

特别值得一提的是电阻场板(SIPOS)(图1-4),该结构最早由Matsushita等人提出。半绝缘的SIPOS层导电能力极其微弱,使得其中的电流水平甚至接近PN结的反向漏电流。

图1-4 电阻场板结构

SIPOS中的电场分布取决于其本身的电阻分压关系,与半导体耗尽区中电场无关,因此在设计中可根据需要调整SIPOS中的电场分布。SIPOS中的恒定电场迫使与之接近的半导体表面耗尽区中电场与之一致,从而基本上避免PN结的表面击穿。

理想的电阻场板可以让PN结的击穿电压与平行平面结的击穿电压相等,实际制造的电阻场板由于离子沾污等问题常出现漏电流过大等问题。

3、场限制环技术

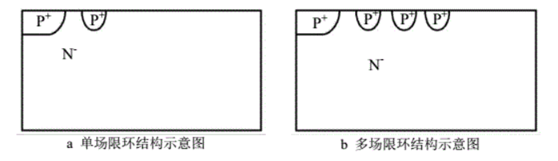

场限制环技术最早由Kao,Y.C等提出,如图1-5所示。

图1-5 场限环结构示意图

场限制环由扩散区构成,它具有与反偏的PN结高掺杂区相同的掺杂类型,但处于电位浮空的状态。在制造中场限制环一般也与PN结高掺杂区采用同一道工序制造完成。

优化设计的场限制环与主结之间的距离应保证环与主结的耗尽区在发生雪崩击穿以前能够汇合,当PN结反偏电压进一步增加时两个空间电荷区便完全合并,这将限制曲面附近电场的进一步增长并使其不能达到PN结的临界击穿电场。

场限制环在一定程度上分担了主结上的压降,有效降低了主结边缘位置的曲率效应。

Adler等人对场限制环电场强度进行了计算。

多维分析表明:环实际所分担的主结电压要比一维分析的结果偏小,采用场限制环后击穿一般不在表面发生,而是发生在曲率最大的点上。

分析结果还表明主结与环之间的距离对环的分压程度有明显影响,而且存在一个场限制环可起作用的最大距离。

此外,场限制环对PN结的作用要比对NP结的作用要好,这是由于半导体表面有形成N型寄生漏电沟道的趋势,使用场限制环的N'P结漏电流较大。

以单环结构为基础又衍生出多环结构,如图1-5(b)所示。多环结构可以通过改变掩膜窗口图形的方式实现,并不增加额外的工序。适当设计的多环结构可使PN结的击穿电压接近平行平面结的击穿电压,但多环将占用芯片更多的面积,这在一定程度上限制了环的数量。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。